# lab 06

# PicoBlaze KCPSM6: interrupts

Digital design – laboratory exercises assistant: Nejc Ilc

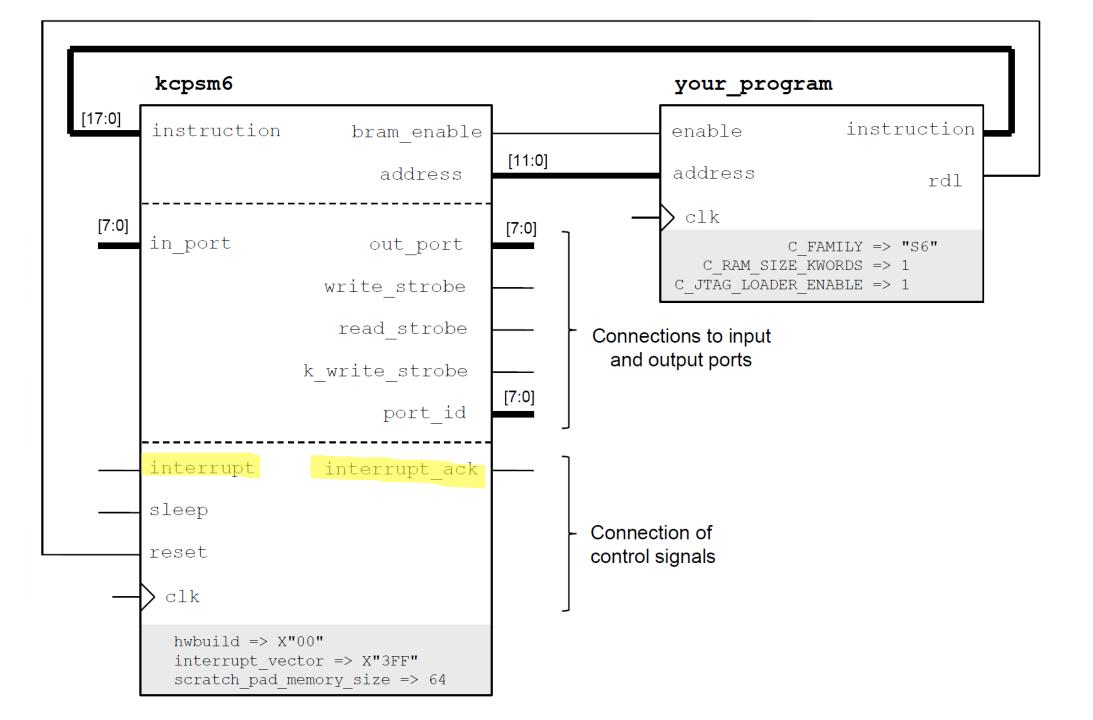

#### Interrupt mechanism

- We connect interrupt source (signal int\_request in a template) to the input interrupt

- there is an interrupt active when interrupt is high

- interrupt should be high for at least two clock cycles

- Signal interrupt\_ack tells us that interrupt has been accepted

- we put interrupt to 0 when interrupt\_ack is high

### Example of the interrupt interface

```

interrupt control: process (clock)

begin

if rising edge(clock) then

if reset = '1' then

interrupt <= '0';</pre>

elsif interrupt ack = '1' then

interrupt <= '0';</pre>

elsif int request = '1' then

interrupt <= '1';</pre>

else

interrupt <= interrupt;</pre>

end if;

end if;

end process;

```

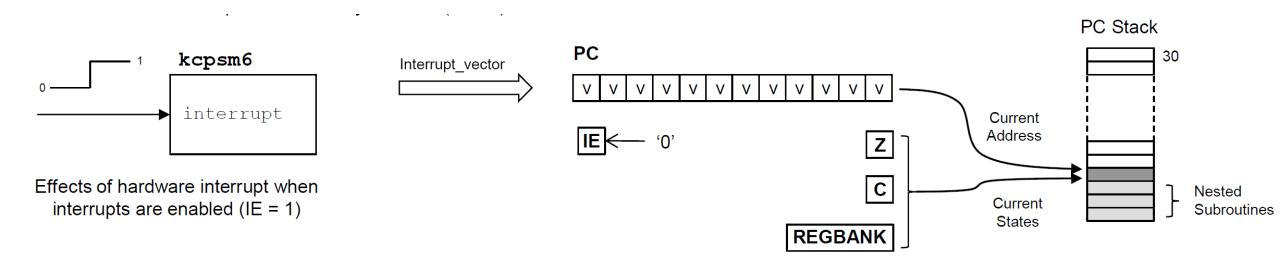

#### **PSM** instructions

- Interrupt Service Routine (ISR) has to start at address 0x3FF

- or as specified by the interrupt\_vector

- Interrupts are disabled by default after the reset/start of processor

- Enabling/disabling interrupts: ENABLE INTERRUPT or DISABLE INTERRUPT

- **Always** when returning from ISR: RETURNI ENABLE or RETURNI DISABLE

### Example

ADDRESS 000 LOAD s0, 07 OUTPUT s0, 01 ENABLE INTERRUPT

- loop: JUMP loop

- isr: ADD s0, 01

OUTPUT s0, 01

RETURNI ENABLE

ADDRESS 3FF JUMP isr

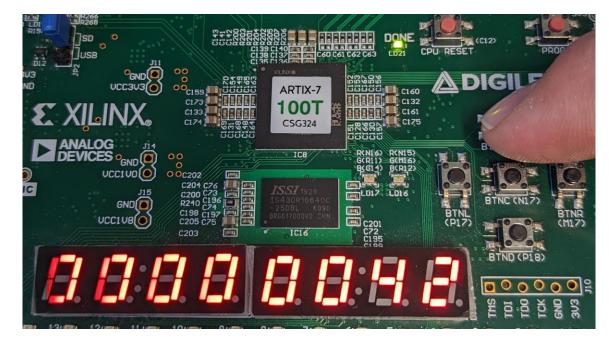

### Challenge

Pressing the top (BTNU) or bottom (BTND) button should trigger an interrupt. The ISR should change the value of the

register that holds the current counter value:

- the counter value is incremented when BTNU is pressed,

- the counter value is decremented when BTND is pressed.

- Show the counter value on a seven-segment display.

- Reset your circuit (and PicoBlaze) with CPU\_RESETN button.